Verilog 轻量化开发环境

Verilog是一种硬件描述语言,用于数字电路的建模和仿真。在Verilog开发过程中,选择合适的开发环境对提高工作效率至关重要。本文将介绍如何搭建轻量化的Verilog开发环境,以提高开发效率。

背景

在Verilog开发中,常用的开发环境有VIAVDO、Sublime Text和VSCODE。VIAVDO体积巨大,编辑器功能有限,仿真速度较慢;Sublime Text是一个功能强大的编辑器,支持各种Verilog插件,但VSCODE由于AI插件的加持,更能提高工作效率,且完全免费。因此,本文将重点介绍如何搭建VSCODE轻量化环境。

环境搭建

首先需要安装VSCODE,可在bing.com搜索并自行安装。

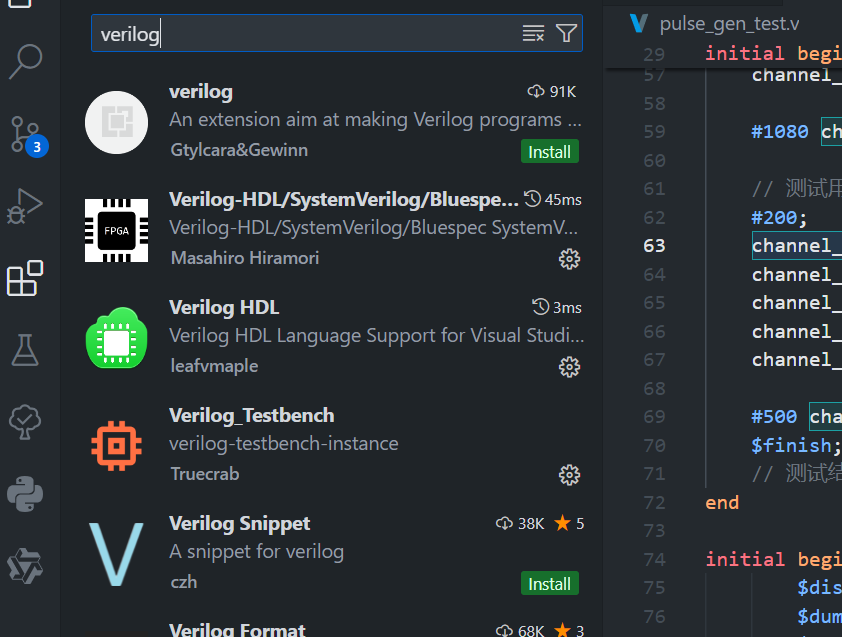

安装插件

图 2‑1 VSCODE Verilog 插件

安装Iverilog

下载并安装轻量级开发、编译工具Iverilog,这样就可以完全不用VIVADO就完成模块级的代码开发。

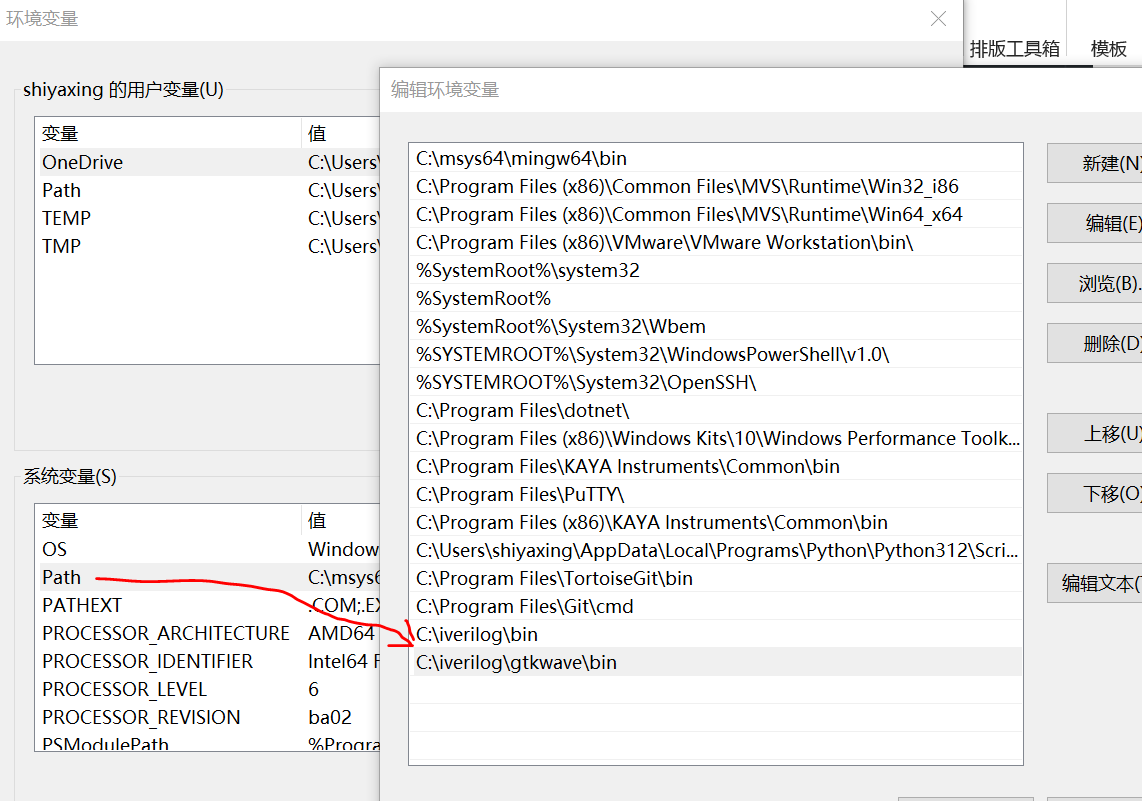

安装完成后,需要设置环境变量:

图 2‑2 设置iverilog 和 gtkwave 环境变量

设置完成后,重启电脑或重启VSCODE。

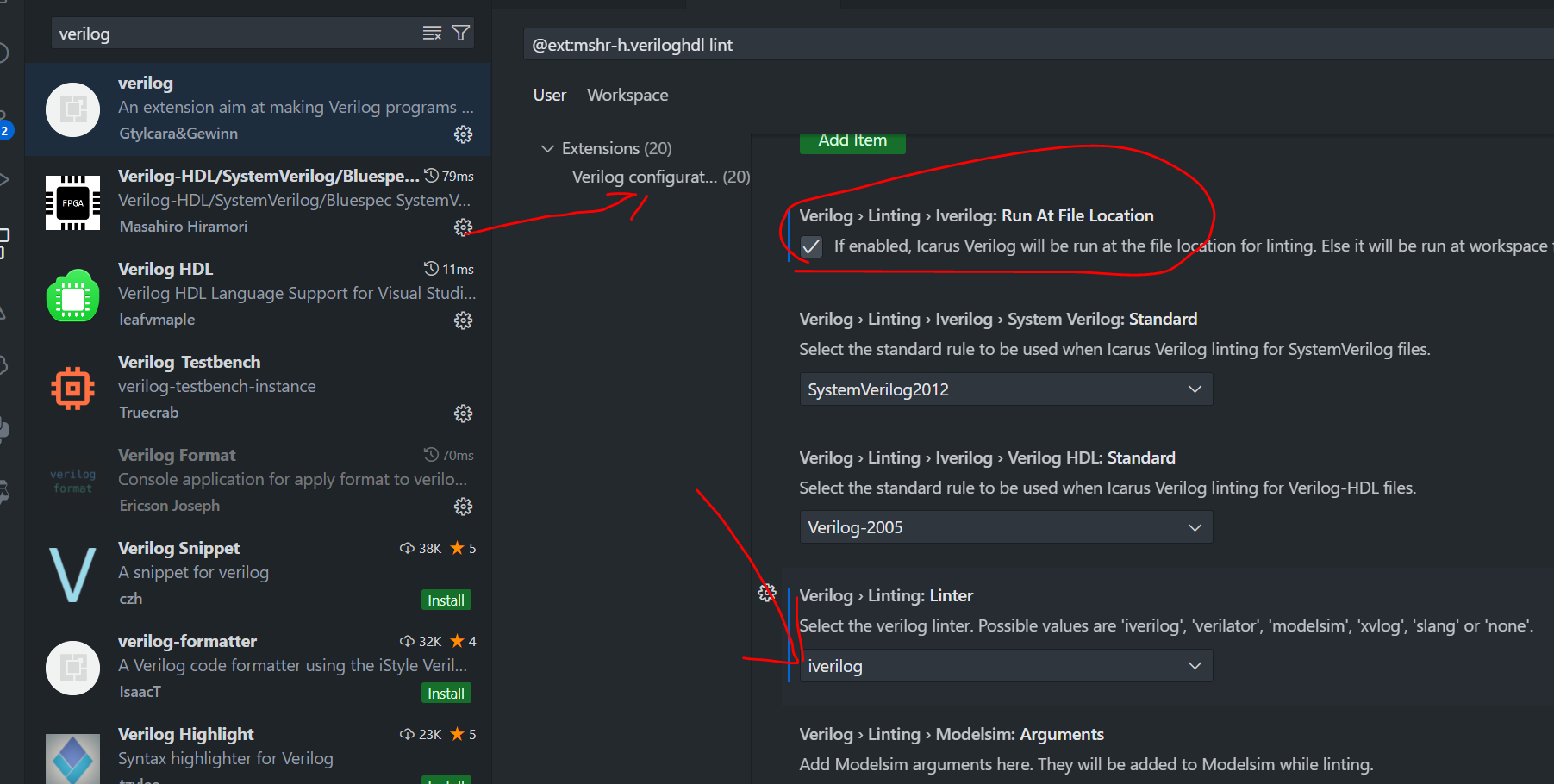

设置插件

图 2‑3 设置linter 为iverilog 运行在文件所在目录

编译 查看波形

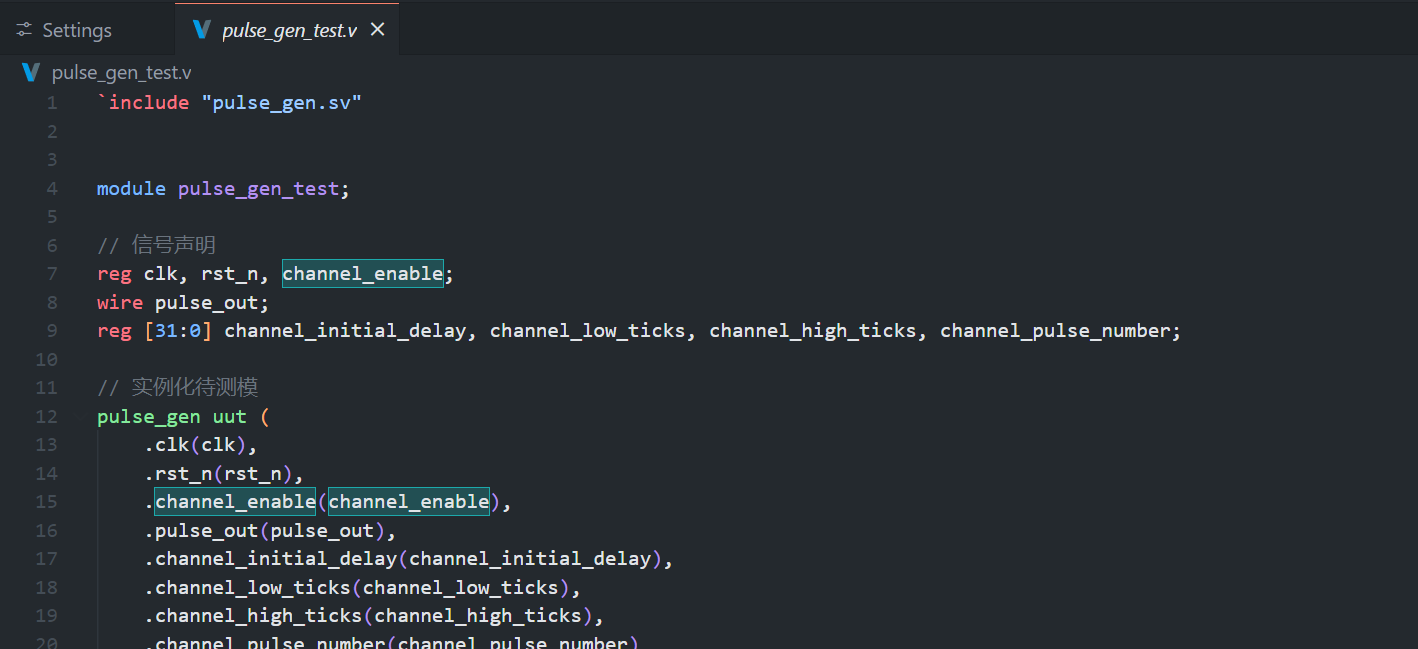

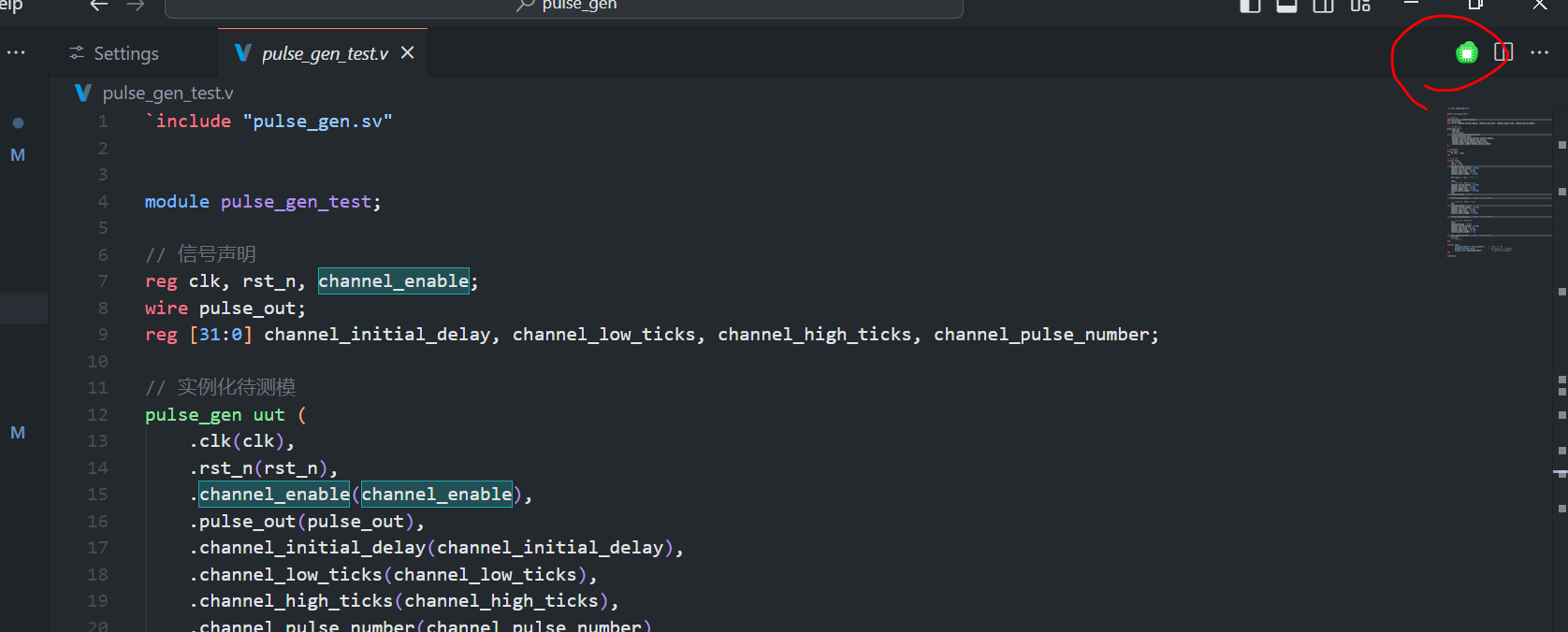

Iverilog对.sv文件支持不好,需要编译的顶层文件最好是.v后缀。涉及到模块调用,最好在代码中用`include声明一下。

图 2‑4 仿真顶层

图 2‑5 运行编译 仿真

注意代码中必须包含自动$finish; 还要dump波形文件。

initial begin

$display("start a clock pulse"); // 打印开始标记

$dumpfile("wave.vcd"); // 指定记录模拟波形的文件

$dumpvars(0, pulse_gen_test); // 指定记录的模块层级

end

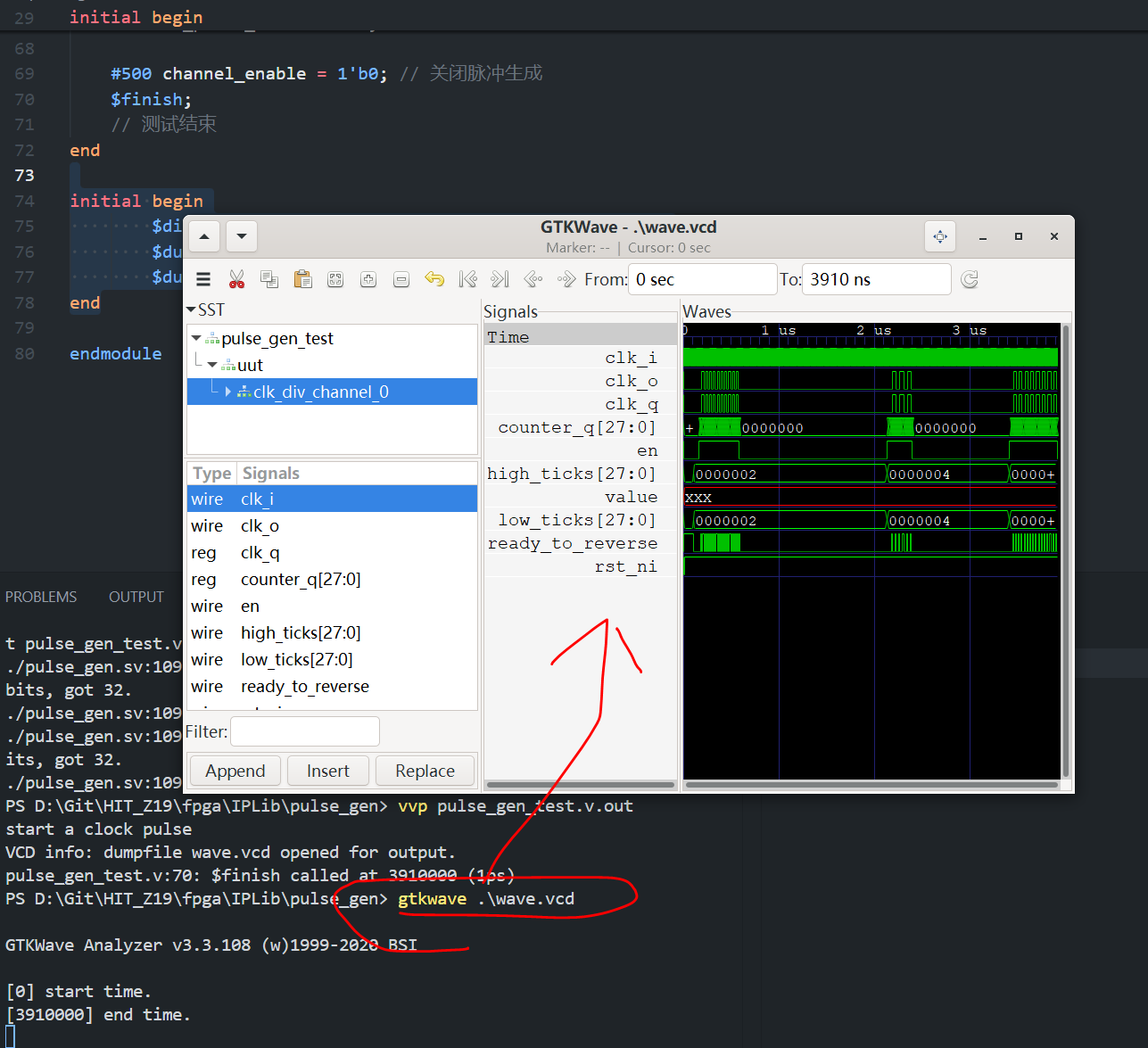

也可以用命令行运行编译和仿真,基本命令如下:

@echo off

iverilog.exe -o target.vvp pulse_gen_test.sv

vvp.exe target.vvp

其中-o是目标文件,pulse_gen_test.sv是待编译的仿真文件,vvp.exe执行对应的仿真。

然后生成目标wave.vcd文件,通过gtkwave可以查看(在终端中执行gtkwave .\wave.vcd)。

图 2‑6 gtkwave 查看波形

需要说明,VSCODE中的自动实例化模块有点问题,希望后面插件可以解决。

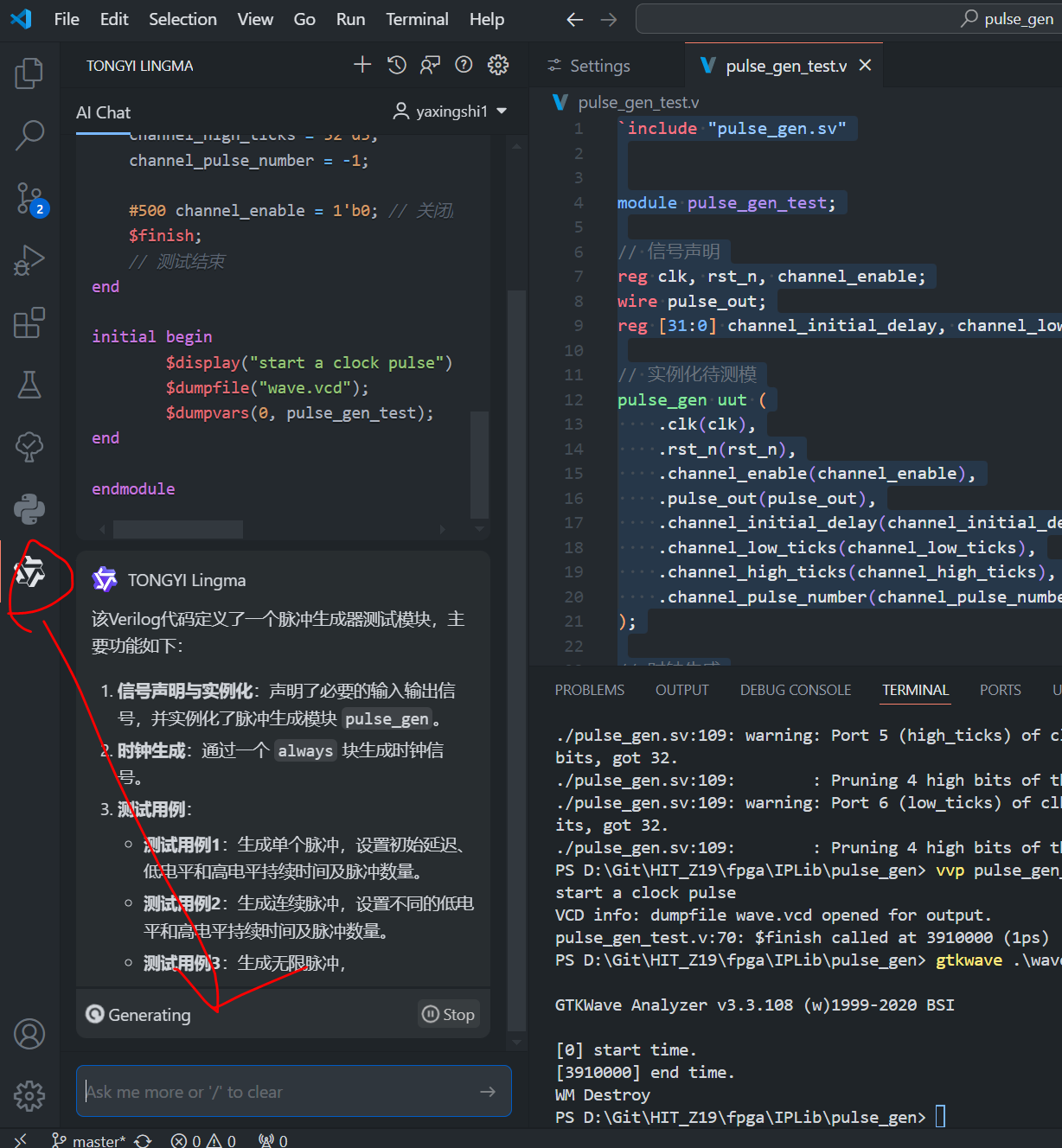

AI 插件

VSCODE最强的是他的AI插件,这个是sublime text 没有的。

图 3‑1 阿里TONGYI Lingma 插件

应用市场搜索安装即可,国内大模型和插件,阿里的最靠谱,实际使用体验不错,详细很快能够追上国外。

以上就是电脑114游戏给大家带来的关于Verilog 轻量化开发环境全部内容,更多攻略请关注电脑114游戏。

电脑114游戏-好玩游戏攻略集合版权声明:以上内容作者已申请原创保护,未经允许不得转载,侵权必究!授权事宜、对本内容有异议或投诉,敬请联系网站管理员,我们将尽快回复您,谢谢合作!